## Department of Electrical and Computer Engineering, UC. EE - 352

## ELECTRONICS II SUMMER QUARTER 2010

## HOMEWORK ASSIGNMENT #5 Due May 12, 2010

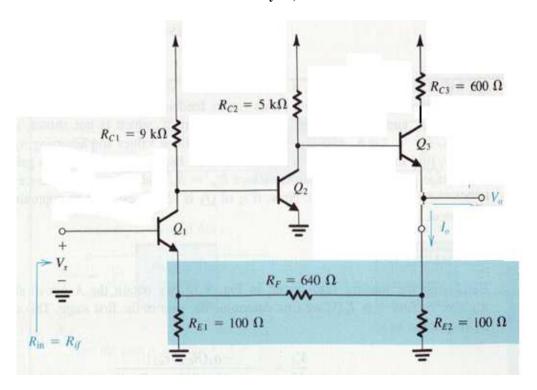

Exercise 8.6. Reconsider the circuit in Fig 8.17(a) (drawn above), this time with the output voltage taken at the emitter of Q3. In this case the feedback can be considered to be of the voltage sampling-series mixing type. Note however that the loop gin remains unchanged. Find the value of  $A=V_{e3}^{'}/V_{s}^{'}$ ,  $A_f=V_{e3}/V_{s}$  and output resistance.

Data:  $I_{C1}$ =0.6mA,  $I_{C2}$ =1mA,  $I_{C3}$ =4mA,  $r_{e1}$ =41.7 $\Omega$ ,  $r_{\pi 2}$ =2.5k $\Omega$ ,  $g_{m2}$ =40mA/V,  $r_{e3}$ =6.25 $\Omega$ ,  $h_{fe}$ =100 for all Qs,  $r_{o}$ =00.

Exersize 8.12. An amplifier with a low frequency gain of 100 and poles at  $10^4$  and  $10^6$  rad/s is incorporated in a negative-feedback loop with a feedback factor  $\beta$ . For what value of  $\beta$  do the poles of the closed loop amplifier coincide? What is the corresponding Q of the resulting second order systems? For what value of  $\beta$  is the maximally flat response is achieved? What is the low frequency closed-loop gain in the maximally flat case?

Problem 8.63. An amplifier has a dc gain of  $10^5$  and poles at  $10^5$ ,  $3.16x10^5$  and  $10^6$  Hz. Find the value of  $\beta$  and the corresponding closed loop gain for which the phase margin of  $45^\circ$  obtained.